1-An address

used by programmers in a system supporting virtual memory concept is called virtual address and the set of such

addresses are called address space.

2-The method

for updating main memory as soon as word is removed fromCache is

called- write-back

3-A control

character is sent at the beginning as well as at the end of each block in the synchronous-transmission

in order to-Supply information needed to separate the incoming bits into

individual character.

4-In non-vectored interrupt, the address of interrupt service routine is -Assigned

to a fixed memory location.

5-Divide

overflow is generated when-Sign of the dividend is same as that of divisor.

6-Which method

is used for resolving data dependency conflict by compiler Itself-Delayed

load.

7-Stack

overflow causes-Internal interrupt.

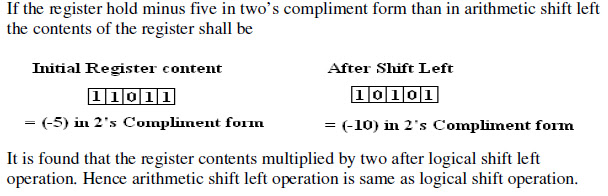

8-Arithmetic

shift left operation-Produces the same result as obtained with logical shift

left operation. For Example-

9-Zero address

instruction format is used for-Stack-organized architecture.

10-Address

symbol table is generated by the-assembler.

11-The

negative numbers in the binary system can be represented by-2's complement

13-ABCD -

seven segment decoder / driver in connected to an LED display.

Which segments

are illuminated for the input code DCBA = 0001. A)b, c

14-How many

flip-flops are required to produce a divide-by-32 device? 5

15-The content

of a 4-bit register is initially 1101. The register is shifted 2 times to the right with

the serial input being 1011101. What is the

content of the register after each shift?- 1110, 0111

16-How many

different addresses are required by the memory that contain 16K words?- 16,384

17-What is the

bit storage capacity of a ROM with a 512' 4-organization?- 2048

18-DMA

interface unit eliminates the need to use CPU registers to transfer data From-Memory to

I/O units

19-How many

128 x 8 RAM chips are needed to provide a memory capacity of 2048 bytes?-16

20-Which of

the following is a self complementing code?-8421

21-Which gate

can be used as anti-coincidence detector?-XOR

22-Which of

the following technology can give high speed RAM?- ECL

23-In 8085

microprocessor how many I/O devices can be interfaced in I/O mapped I/O

technique?- 256 input devices & 256 output devices.

24-After

reset, CPU begins execution of instruction from memory address-0000H

25-Which is

true for a typical RISC architecture?- Micro programmed control unit.

26-When an

instruction is read from the memory, it is called-Fetch cycle

27-Which

activity does not take place during execution cycle?- Branch address is

calculated & Branching conditions are checked.

28-A circuit

in which connections to both AND and OR arrays can be programmed is

called-RAM

29-If a

register containing data (11001100)2 is subjected to arithmetic shift left operation,

then the content of the register after 'ashl' shall be-(10011000)2

30-Which logic

is known as universal logic? NAND logic.

No comments:

Post a Comment